提供七进制加法计数器电路设计的内容摘要:七进制计数器电路设计

数字信号处理上机实验报告学号: 姓名:实验题目一1. 实验要求:序列卷积计算(1)编写序列基本运算函数,序列相加、相乘、翻转、求和。非门、a、b构成频率发生器,产生一固定频率的脉冲送到d触发器的时钟端c,以触发d触发器组成的脉冲分配器。60进制计数器由74ls160构成的60进制计数器,将一片74ls160设计成10进制加法计数器,另一片设置6进制加法计数器。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

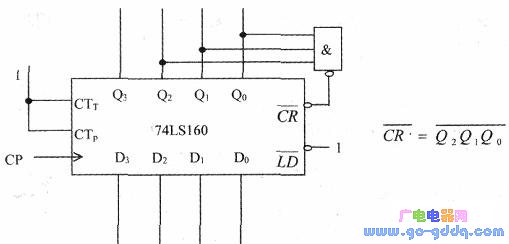

七进制加法计数器电路设计 - N 进制计数器仿真设计 1.设计要求 试分别采用反馈清零和反馈置数的方法,用同步十进制加法计数器 74LS160(或同步 4 位二进制加法...

工程学院 专业 学号 脉冲序列发生器(1010101010) 电子信息科学与技术 内容及要求: 1.利用触发器和逻辑门电路,设计七进制同步加法计数器,和脉冲序列发生器 (...

对于奇数分频 ,当 n 计数器进位时 ,需对时钟 cp进行反相 , 所以反相控制信号 q可以由以下状态方程式给出:n+q1= cp′ 综合前述 ,利用脉冲周期剔除法可实现分频系数 k =2n- odd 的 50 % 占空比整数分频。如果只是手工相减,完全可以借鉴十进制数的减法,不用涉及反码补码之类的概念。 三、实验平台 1、硬件:eda 试验箱、带并口 pc 机 2、软件:windows xp 操作系统、muxplus ii 10.2 四、方案设计及实现 1、系统实现原理和总体框图 数字钟电路实际上是一个对标准 1hz 进行计数的计数电路,秒计数器满 60 秒后向分计数器进位,分计数器满60 秒后向时计数器进位,时计数器按24 翻 1 规律计数,计数输出经译码后送到 led 显示器,由于计数的起始时间不可能与标准时间(北京时间)一致,故需要在电路上加上一个校时电路,如图4-1 所示为简易数字钟的构成框图。cd4026同时具有显示译码功能,可将计数器的十进制计数转换为驱动数码管显示的七位显示码,省去了专门的显示译码器。

实验774ls90任意进制计数器 - 实验七 任意进制计数器 一 实验目的 1.了解中规模集成电路的逻辑功能和各控制端的作用。 2.熟悉集成计数器74LS90的级联扩展。 3...

JK触发器实现7进制计数器 - 用JK触发器 设计一个七进制计数器,要求它能自启动。 已知该计数器的状态转换图及状态编码如图所示。74ls161 7进制计数器74ls161 7进制计数器 解:由给出的状态转换图可画出...

在集成电路(integrated circuit,简称ic)进入超大规模集成电路时代,可测试性设计(design for testability,简称dft)是电路和芯片设计的重要环节,它通过在芯片原始设计中插入各种用于提高芯片可测试性(包括可控制性和可观测性)的硬件逻辑,从而使芯片变得容易测试,大幅度节省芯片测试的成本。5、veriloghdl设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,clk是时钟输入端,上升沿有效。原理与常用ralink8187l芯片不同,无线网络接收器常采用低辐射高灵敏度雷凌3070芯片,价格昂贵,同时配备了密码破解软件。

54/74hc4538双可重触发单稳态触发器 逻辑符号图 符号框图及外接r、c连线图 rext/cext和cext的引脚分别与 电容元件相连,不属于逻辑状态 连接,故在逻辑符号图引线上 用“X”号表示。 其逻辑框图如下: 图 1-1 74ls00 的逻辑图图 1-2 iis的测试电路图 ttl 集成与非门的主要参数有输出高电平 voh、 输出低电平 vol、 扇出系数 n0、电压传输特性和平均传输延迟时间 tpd 等。

支持