卷积滤波器 适用于工业物联网的高效机器视觉应用的图像处理系统设计(2)

image = cv :: imread(“image.bmp”);

镜像图像的简单操作可以通过声明一个新的Mat对象来实现 - 例如“镜像” - 并发出命令cv :: flip(image,mirrored,1)。第三个位置使用的整数决定了图像翻转的轴。

Mat数组提供对图像数据的低级别像素访问,以支持扫描区域以查找属性(例如最小值或最大值)的算法,并支持直接操作数据。但是该库还实现了在机器视觉中有用的更高级过滤功能,例如边缘检测过滤器。例如,cv :: Sobel和cv :: Laplacian调用实现了对图像的滤波器,该图像通过将图像数据与3×3或更大的矩阵进行卷积来检测像素亮度的突然变化。在源阵列上执行过滤器会生成包含可能边缘的数组。较大的内核可用于抑制高频噪声并以更高的置信度产生实际边缘。使用Canny算子等函数进行阈值处理可以提高结果的整体质量。

可以使用cv :: HoughLinesP等函数提取图像中检测到的行,并用于支持对其进行操作的算法在源图像中找到的形状。这些可用于确定是否存在预期在图像中的物体,例如发动机壳体上的紧固件。

虽然OpenCV是为计算效率而设计的,但是高分辨率的数据流量相机可以挑战纯软件实现,甚至是那些在高性能多核SoC上运行的软件。 OpenCV不仅支持在通用处理器上实现其功能,还支持在图形处理单元(GPU)甚至自定义硬件上实现其功能。保持基于软件的控制的灵活性,同时利用硬件实现下可实现的性能的一种方法是采用可编程逻辑。 Xilinx Zynq-7000提供了一种在单个SoC中访问多核CPU和可编程逻辑的便捷方式。

Zynq-7000平台将一个或两个ARM??Cortex??-A9处理器与灵活的硬件组合在一起。嵌入式现场可编程门阵列(FPGA)以及支持高速I/O的外设。 Zynq-7000器件支持两种形式的FPGA架构:一种基于Xilinx Artix-7架构,另一种基于高性能Kintex-7架构。所有这些都采用28 nm CMOS工艺实现,具有高性价比的高逻辑和存储密度。

除了基于查找表概念的灵活可编程逻辑外,Artix和Kintex架构均提供数字信号处理(DSP)资源设计用于有效处理滤波器和卷积。使用片式架构,DSP资源可以调谐到器件,Kintex提供比Artix更高的DSP引擎与位级逻辑比。超过2000条互连线将处理器复合体连接到可编程结构,有助于支持在处理模块之间传输图像数据所需的高带宽。

使用Zynq-7000平台的设计人员可以使用高级别Vivado Design Suite中的综合(HLS)技术将算法编译成可编程硬件。卷积滤波器传统的FPGA开发是围绕硬件描述语言(HDL)构建的,例如Verily和VHDL。尽管这些HDL分别与C和Ada具有语法上的相似性,但它们的运行细节水平低于大多数软件开发人员所熟悉的程度。 Verilog和VHDL基于位级操作和组合逻辑。 HLS技术提供了将用C ++等语言表达的算法转换为硬件的能力。

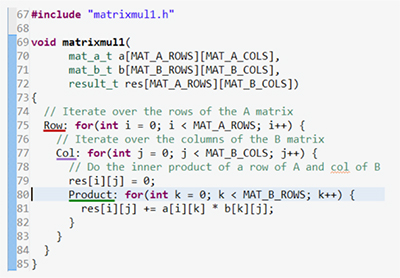

HLS综合利用面向对象的C ++基础,让程序员识别并发机会,在代码中进行低级调度,为合成引擎提供如何从源代码生成硬件的方向。例如,创建用于在FPGA架构上部署的嵌套矩阵乘法运算的程序员可以识别可以在Vivado HLS实现工具中分配给硬件及其相关调度的每个循环的处理模块。在图1中,Row,Col和Product标识符表示输出块。图2显示了Row块及其包含的Col块的扩展,以及用于在块之间移动数据的两个区域。控制流循环显示合成操作的延迟。

图1:适用于FPGA实现的嵌套循环代码。

第二